Wikipedia quotes this statement from Intel's manual

The functionality of A20M# is used primarily by older operating systems and not used by modern operating systems. On newer Intel 64 processors, A20M# may be absent.

It is a phrase that it is actually in the manual nowadays but it is ambiguous:

- Does

A20M#actually refer to the pin only or to the whole masking thing? - The A20M event/interrupt is named in the description of many instructions (e.g. TXT

GETSECor VMX instructions).

What I do know

The A20M# pin itself is gone, it was at some time replaced by the VLW (Virtual Legacy Wire) interface within the DMI. The DMI protocol is rich enough to have messages for asserting various legacy pin:

The PCH supports VLW messages as alternative method of conveying the status of the following legacy sideband interface signals to the processor: • A20M#, INTR, SMI#, INIT#, NMI

This quote comes from the PCH series 8 (Haswell era).

The PCH, up to these days, has an A20GATE Pass-Through functionality.

When the PCH is configured to trap the access to the legacy 8042 IO ports (60h, 64h) and deliver an SMI instead (for PS2 simulation of USB keyboards/mice), it can optionally let the A20 line enable sequence go through without being trapped.

Depending on how the PCH is configured, this allows either the EC (mobiles) or the SuperIO chip (desktops) to be the target of the command sequence.

Curiously enough, the PCH series 8 (Haswell era) datasheet, reports:

Note: A20M# functionality is not supported.

In the LPC section (where the EC/SuperIO are attached to), this, however, may only mean that the PCH itself doesn't emulate the A20 gate and an external chip (EC or SuperIO) must handle it.

It that were the case, the PCI must have a pin to be asserted by the external chip. The datasheet didn't mention any.

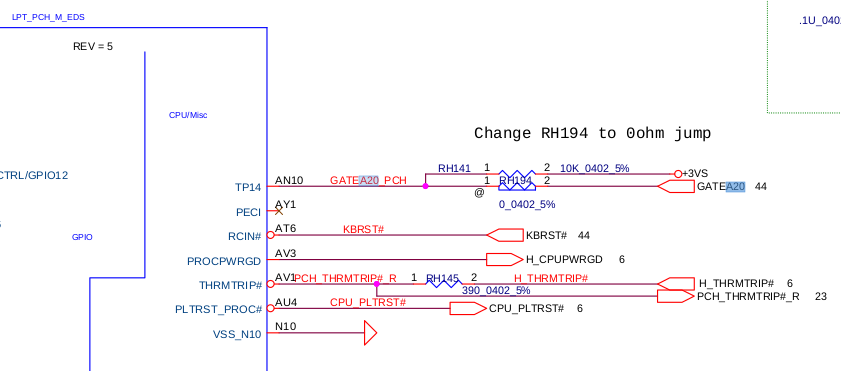

However, I've found the schematic of my previous Haswell laptop somewhere on a Chinese site and the schematic shows that the pin (actually the ball) AN10 (a.k.a. TP14) is used as the A20M input pin:

The blu box on the left is labeled as LYNX-POINT-DH82LPMS_BGA695.

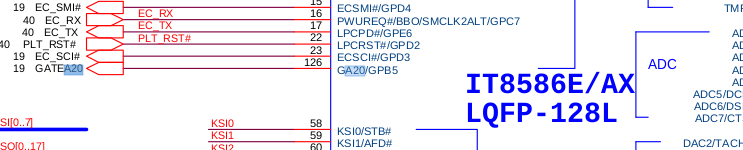

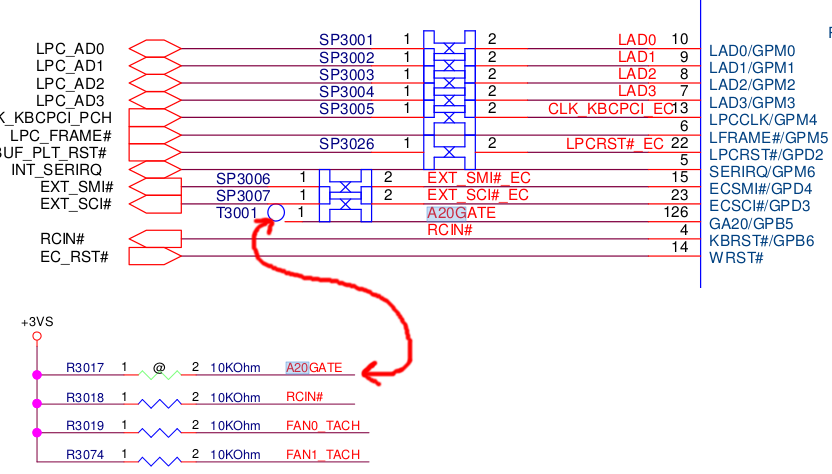

The other end of the GATEA20 signal comes from the EC (as expected):

The IT8586E/AX is an EC from Lenovo (apparently).

So the A20 line could still be masked off on Haswell platforms, unless I misinterpreted the schematics.

Thus, the datasheets are not complete regarding the A20M aspect. Probably the Intel's BIOS Writer Guide has it all.

What I want to know

Can the A20 line be disabled on, at least one, Haswell platform? What about Skylake and successors?

What I have done

I wrote a simple legacy boot loader that checks if the A20 line is enabled and try to disable it:

- If the A20 line is disabled, the test ends. The A20 gate functionality exists on the test platform.

- Otherwise, it asks the BIOS the supported A20 gate methods and then ask it to disable the A20 line (I trusted OSDev for the nomenclature of the functions, i.e. the enable vs disable-of-what thing, so I hope that call disables the A20 line and not the masking)

- In case the BIOS returned an error, the program disables the A20 line through the KBC, with the fast a20 method and with the port

0eehmethod. - Test again the A20 line status. If it is still enabled, disable it manually (unless it was done already) and test it once more.

When I run this on my Skylake laptop, the BIOS returned that only the fast A20 method was supported and signaled no error but yet the A20 line was still enabled. Even aver manually disabling it, the A20 line was still enabled.

I concluded that the A20 line cannot be disabled on Skylake, i.e. it doesn't exist anymore.