Hi I'm writing a kernel and plan to use MSI interrupt for PCI devices.

However, I'm also quite confused by the documentations.

My understanding about MSI are as follow:

From PCI device point of view:

- Documentations indicate that I need to find Capabillty ID = 0x05 to locate 3 registers: Message control (MCR), Message Address (MAR) and Message Data (MDR) registers

- MCR provide control functionality for MSI interrupt,

- MAR provide the physical address the PCI device will write once interrupt occurs

- MDR forms out the actual data it will write into the physical address

From CPU point of view:

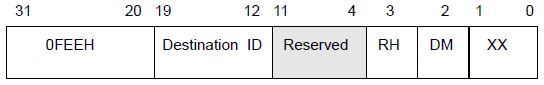

Documentation shows that Message Address register contains fixed top of 0xFEE, and following by destination ID (LAPIC ID) and other controlling bits as follow:

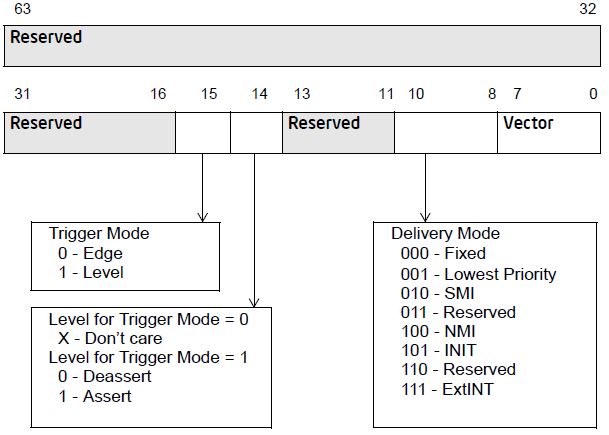

The Message Data register will contain the following information, including the interrupt vector:

After reading all of these, I am thinking if the APIC_ID is 0x0h would the Message Address conflict with the Local APIC memory mapping? Although the address of FEE00000~FEE00010 are reserved.

In addition, is it true that the vector number in MDR is corresponding to the IDT vector number. In other words, if I put MAR = 0xFEE0000C (Destination ID = 0, Using logical APIC ID) and MDR = 0x0032 (edge trigger, Vector = 50) and enable the MSI interrupt, then once the device issues an interrupt CPU would correspondingly run the function pointed by IDT[50]? After that I write 0h to EOI register to end it?

Finally, according to the documentation, the upper 32 bit of MAR is not used? Can anyone help on this?

Thanks a lot!