The fsm_export command operates on extracted FSMs (i.e. $fsm cells). In order to create a state where the design contains such FSM cells, you first need to detect FSMs (fsm_dectect) and then extract them (fsm_extract). See help fsm for more information on the FSM flow.

The easiest way to get to such a state is to simply run fsm -nomap. Example script:

read_verilog test.v

proc; opt; fsm -nomap

fsm_export -o test.kiss2

For example consider for the following test.v file.

module test(input clk, rst, ctrl, output [3:0] O);

reg [1:0] state;

always @(posedge clk) begin

O <= 0;

if (rst) begin

state <= 0;

end else case (state)

0: begin

state <= ctrl ? 1 : 2;

O <= 1;

end

1: begin

O <= 2;

if (ctrl) begin

state <= 2;

O <= 3;

end

end

2: begin

O <= 4;

if (ctrl) begin

state <= 3;

O <= 5;

end

end

3: begin

if (!ctrl)

state <= 2'b00;

end

endcase

end

endmodule

The script above will produce the following test.kiss2 file. (I have just fixed a bug in fsm_detect, so use current git head.)

.i 2

.o 3

.p 12

.s 4

.r s0

-1 s0 s0 100

00 s0 s1 100

10 s0 s2 100

-1 s1 s0 001

00 s1 s1 001

10 s1 s3 001

-1 s2 s0 010

10 s2 s1 010

00 s2 s2 010

00 s3 s0 000

-1 s3 s0 000

10 s3 s3 000

Note: The FSM outputs in this case are not directly the four O signal bits. Instead Yosys created an FSM with a three bit output and an encoder outside of the FSM for creating the four O signal bits.

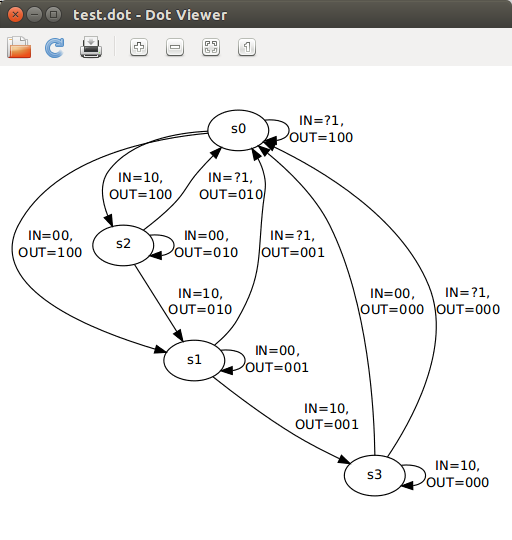

Regarding visualization: Unfortunately I don't know of any GUI tool to display KISS2 files (which does not mean that no such tool exists). But it is quite easy to create a GraphViz .dot file from a KISS2 file, for example using the following python script (kiss2dot.py).

#!/usr/bin/env python3

import fileinput

print("digraph fsm {")

for line in fileinput.input():

if not line.startswith("."):

in_bits, from_state, to_state, out_bits = line.split()

print("%s -> %s [label=\"IN=%s,\\nOUT=%s\"];" % (from_state, to_state,

in_bits.replace("-", "?"), out_bits.replace("-", "?")))

print("}")

Example usage:

python3 kiss2dot.py test.kiss2 > test.dot

xdot test.dot

This will display the following graph:

![xdot output]()