I am getting some unexpected behavior when using the to_01 conversion function in VHDL-2008. My expectation would be that vector bits that can clearly be interpreted as high or low are mapped to '1' and '0' respectively. The remaining vector bits should be converted to '0' bits.

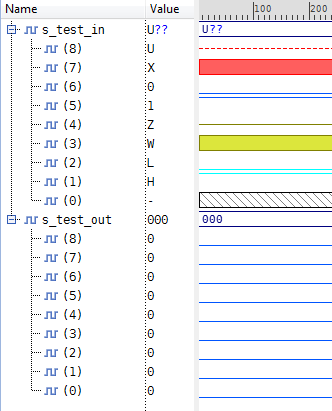

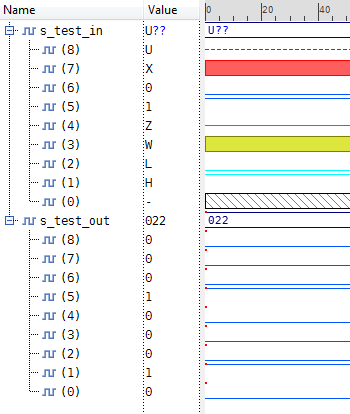

However, with the code depicted below, I get the whole vector converted to all '0's.

Is this behavior correct? Or is this a bug in the simulator software (ALDEC Riviera-PRO)?

Is there any IEEE function that meets my expectations or do I have to write my own function to achieve that?

library ieee;

use ieee.std_logic_1164.all;

entity test_to_01 is

end entity test_to_01;

architecture rtl of test_to_01 is

signal s_test_in : std_logic_vector(8 downto 0) := "UX01ZWLH-";

signal s_test_out : std_logic_vector(8 downto 0);

begin

s_test_out <= to_01(s_test_in);

end architecture rtl;