We all know that when looking at source code it's a safe assumption that the direction flag will be clear. The probability of the direction flag is very low.

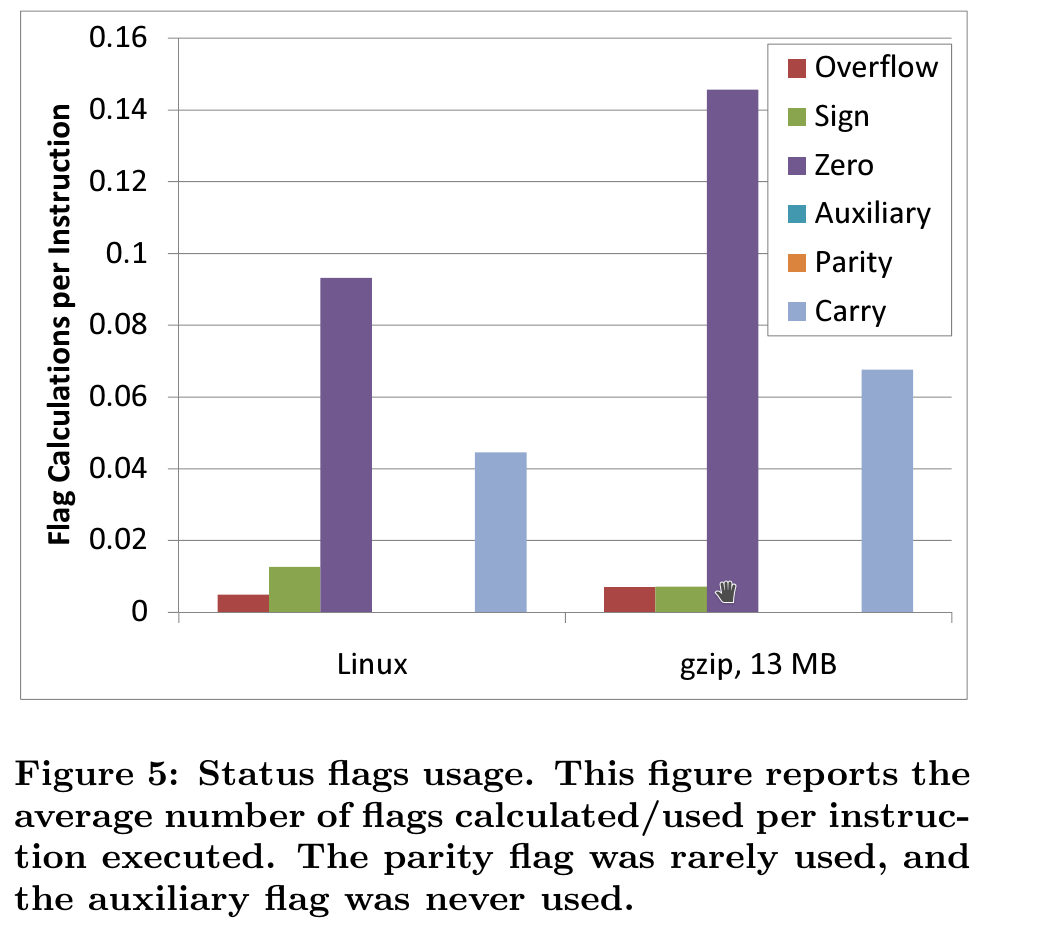

I wanted to find out about the probabilities of the other flags. That's why I wrote a test program that single steps some of my existing software, incrementing a counter for each of the first 12 EFLAGS bits.

Results confirm the assumption made about the direction flag (DF) and, not surprisingly, show that the probability of the overflow flag (OF) is very low.

But what about the other flags? The carry flag (CF), auxiliary flag (AF), zero flag (ZF), and sign flag (SF) seem to settle at 25%, but the parity flag (PF) jumps out at well over 50%.

I'd like to know why the probabilities of CF, AF, ZF, and SF are so low.

For the PF, my own two cents explanation tells me that, given the 50-50 distribution of parity even and parity odd in all possible 8-bit bitpatterns and realizing that a couple of the most frequently used numbers (0 and -1) have parity even, a more than 50% chance is reasonable.

mov, which don't affect flags? I got the idea it would be somehow more interesting if you would check the flag only when the instruction did affect it, although I have no idea why it sounds interesting and what would be benefit of that. Basically if you have CF=1 across larger area ofmov, you count it several times, while the code is not relevant to the CF content. About PF - I agree, probably the zero alone will skew it enough to be above 50% most of the time. – Nellanelldauint64_twith numbers that are not large will often clear CF (I think). Signed values crossing zero will set CF, but it can be rare to actually have negative numbers even when using signed types. – Sluiteradd/submay often be aligned, leaving the low couple bits of a reg clear, biasing PF somehow... Or maybe just some specific numbers come up a lot, and they happen to set PF. – Sluiter