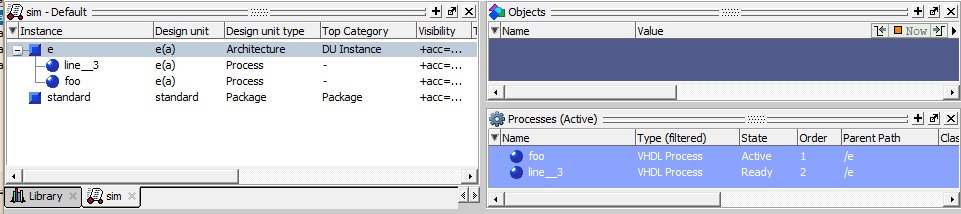

You can use labels to identify things in a simulator as JHBonarius says, but there are other uses for labels, too:

i) Identifying the end of a long block of code, eg

my_if : if A = B then

-- lots of lines of code

end if my_if;

ii) keeping track of complicated code, eg

my_if_1 : if A = B then

my_if_2 : if A = B then

my_if_3 : if A = B then

my_if_4 : if A = B then

my_if_5 : if A = B then

my_if_6 : if A = B then

-- blah blah blah

end if my_if_6;

end if my_if_5;

end if my_if_4;

end if my_if_3;

end if my_if_2;

end if my_if_1;

iii) It is usually a good idea to label assertions so that they can be easily identified in an EDA tool, eg :

enable_check : assert enable = '1';

iv) If you label something, then you can decorate it with an attribute (ie attach some metadata for some other EDA tool), eg something like this might stop a synthesiser optimising something away:

attribute KEEP : boolean;

attribute KEEP of g0:label is TRUE;

...

g0 : CLK_EN port map ( ...

(The exact names will depend on the synthesiser.)