I've a heard a lot about Altivec registers but I don't even find it on a POWER9 ISA. On that document I only find VR and VSR registers under Chapter 6 "Vector Facility" and Chapter 7 "Vector-Scalar Floating-Point Operations".

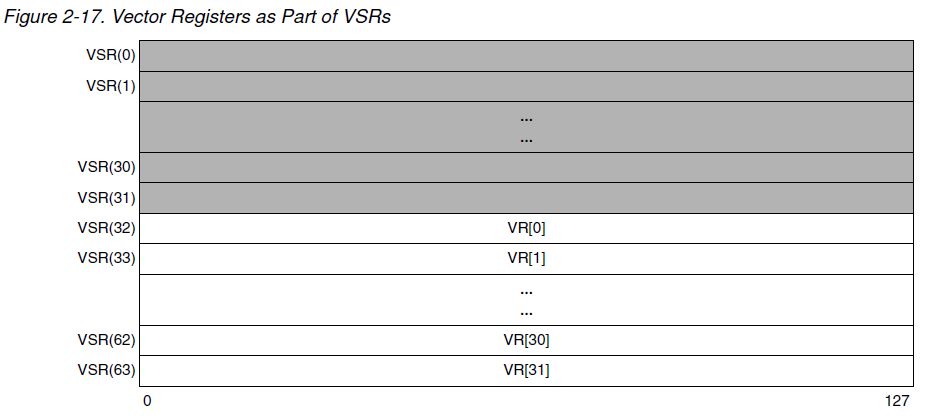

On ABI I noticed how the registers are physically allocated:

and I still didn't get why there are 2 groups. Is Altivec legacy?

As far as I understood, the following is what happened:

- Altivec / VMX (Vector Multimedia eXtensions) is an old SIMD technology for PowerPc. I see it as the old Intel MMX.

- The new VSX (Vector Scalar eXtensions) are an upgrade of it but to avoid breaking compatibility with Altivec, they remained 32 registers (VSR32-VSR63) only and Altivec operations can't handle the other VSR0-VSR31. The VSX instructions, however, can operate on all 64 registers (VSR0-VSR63). I see it as the new Intel SSE.

Is that correct?