It is using IA-32e paging.

A logical processor uses IA-32e paging if CR0.PG = 1, CR4.PAE = 1, and IA32_EFER.LME = 1.

With IA-32e paging, linear address are translated using a hierarchy of in-memory paging structures located using the contents of CR3.

IA-32e paging translates 48-bit linear addresses to 52-bit physical addresses.

Although 52 bits corresponds to 4 PBytes, linear addresses are limited to 48 bits; at most 256 TBytes of linear-address space may be accessed at any

given time.

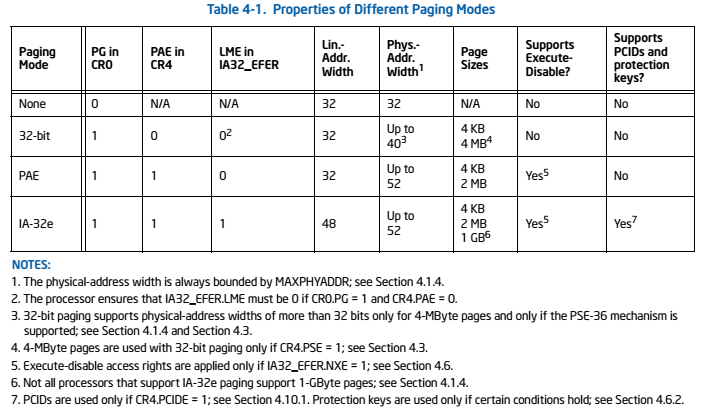

x86 processors supports three paging modes:

- 32-bit paging (CR0.PG = 1 and CR4.PAE = 0)

- PAE paging (CR0.PG = 1, CR4.PAE = 1, and IA32_EFER.LME = 0)

- IA-32e paging (CR0.PG = 1, CR4.PAE = 1, and IA32_EFER.LME = 1)

A table summarising the differences is reported here (as image, unfortunately)

![Differences between the three paging modes on x86]()