There isn't any instruction that treat eflags as read-write GP-register.

Quoting Intel1:

Some of the flags in the EFLAGS register can be modified directly, using special-purpose instructions (described in

the following sections). There are no instructions that allow the whole register to be examined or modified directly.

The following instructions can be used to move groups of flags to and from the procedure stack or the EAX register:

LAHF, SAHF, PUSHF, PUSHFD, POPF, and POPFD. After the contents of the EFLAGS register have been transferred to

the procedure stack or EAX register, the flags can be examined and modified using the processor’s bit manipulation

instructions (BT, BTS, BTR, and BTC).

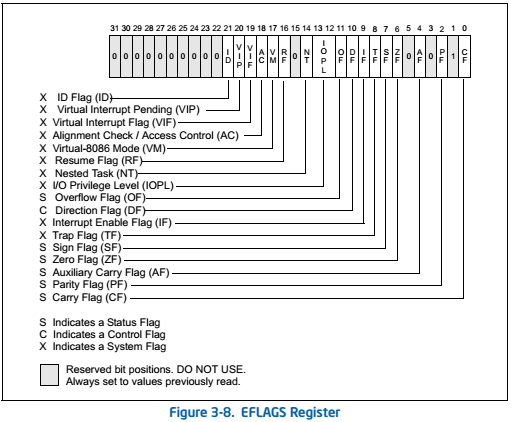

The eflags register is divided into three groups: Status flags, Control flags and System flags.

![eflags content]()

Of the Status flags only the CF can be manipulated directly with clc, stc, cmc.

There is no instruction to read the CF but you can read it indirectly with instructions like cmovcc, adc, setcc.

All other flags need to be modified with specially tailored arithmetic instructions or by coping the Status group content of eflags into ah (with lahf) or the stack (with pushfd) and than back into eflags (with sahf or popfd).

In the Control flags group there is only DF that can be manipulated with cld and std.

To read the current value of DF you need to use pushfd.

The System flags are usually manipulated indirectly by performing some privileged operation like switching a task, entering v86 mode and similar.

The IF can be manipulated directly with cli and sti.

All other flags can only be manipulated with pushfd/popfd.

For reference:

- In 64-bit mode the flag register is

rflags but the higher 32 bits are reserved so far, thereby rflags is handled as eflags.

pushfd pushes eflags on the stack. There is also a 16-bit version pushf that pushes only the lower 16 bits of eflags. Same for popfd/popf. lahf/sahf only copies the status flags.

1 Intel Manuals, Volume 1, Section 3.4.3.

clcis perfect fit for you. If you have a need to change flag (RCL is a valid need), then it's very likely the CPU has some way, the instruction set as whole is nicely working together (although sometimes it's not obvious). – Hame