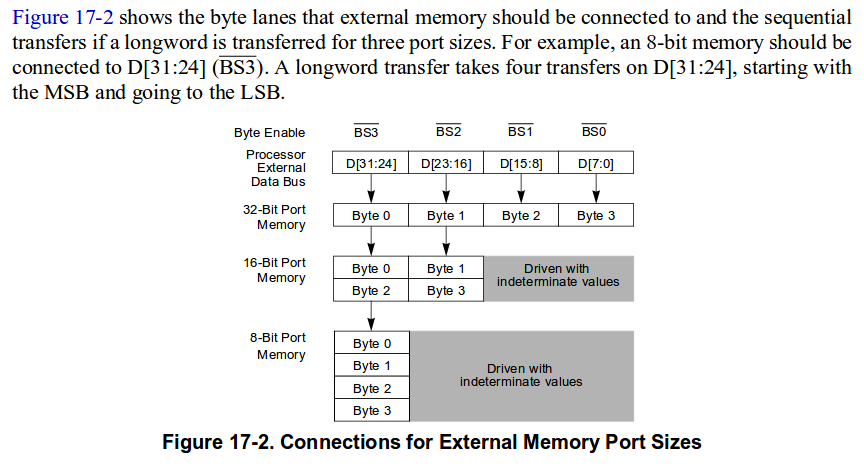

The MCF5271 manual discusses the external interface of the processor in Chapter 17. The processor implements a byte-addressable address space with a 32-bit external data bus. The D[31:0] signals represent the data bus, the A[23:0] signals represent the address bus, and the BS[3:0] (active low) signals represent the byte enable signals. Even though the the data bus 32-bit wide, the memory module connected to it can be 32-bit, 16-bit, or 8-bit wide. This is referred to as the memory port size. Figure 17-2 from that chapter shows how all of these signals are related to each other.

![enter image description here]()

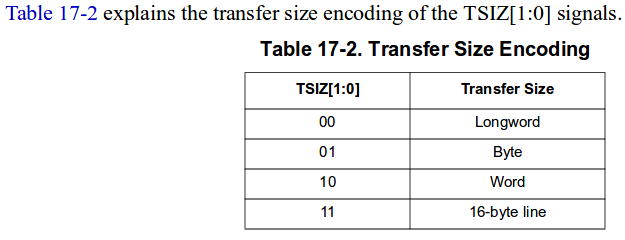

Table 17-2 from the same chapter shows the supported transfer sizes (Specified by a signal called TSIZ[1:0]).

![enter image description here]()

The A[0] and A1 address signals specify the alignment of the transfer. Memory alignment is defined in Section 17.7 of the same chapter.

Because operands can reside at any byte boundary, unlike

opcodes, they are allowed to be misaligned. A byte operand is

properly aligned at any address, a word operand is misaligned at an

odd address, and a longword is misaligned at an address not

a multiple of four. Although the MCF5271 enforces no alignment

restrictions for data operands (including program counter (PC)

relative data addressing), additional bus cycles are required for

misaligned operands.

Putting all of that information together, we can easily determine how many cycles are required to transfer a 1-byte, 2-byte, 4-byte datum to any memory location (aligned or misaligned) through a memory port of size 1-byte, 2-byte, or 4-byte.

Let's consider the example from the image you've attached. How to store a longword at address 0x0000003 through a 32-bit memory port? Focus on the rows where the port size is 32-bit. We have A[1:0] = 11. So first a single-byte transfer must be performed with BS[3:0] = 1110. The other three bytes need to be transferred to locations 0x0000004 (A[1:0] = 00), 0x0000005 (A[1:0] = 01), and 0x0000006 (A[1:0] = 10). This can be done using either three single-byte transfers (which would take three cycles) or using a single two-byte transfer followed by a single one-byte transfer (which would take two cycles).