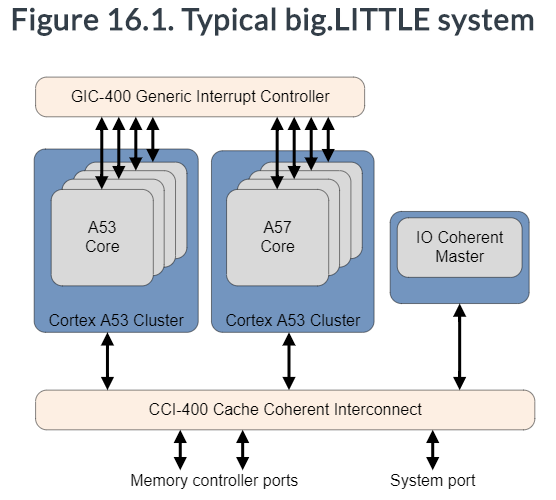

As far as I know, big cores and little cores are in separate clusters on big.LITTLE system. And cache coherence between clusters requires the regions are marked as Outer Shareable and is very expensive. I have checked the Linux kernel code, and seems it only requires coherence in Inner Shareable domain. So my question is how can Linux guarantee cache coherence in 'CPU migration' or 'Global Task Scheduling' models where both clusters are active at the same time?

How is cache coherency maintained on ARMv8 big.LITTLE system?

what did arms documentation say and what did the chip vendors documentation say? –

Pleuro

how would it be different with respect to managing coherency within one of the A53 cores? –

Pleuro

Managing coherency within one of the A53 cores is not a problem. But what if a thread migrates to a A57 core in another cluster in case of GTS? –

Butch

The coherency within one cluster is the problem, the external whether it has its own next layers of cache or not is just external, and that extends to however many clusters you have. You solve the micro you have solved the macro. –

Pleuro

I have got the answer from the arm comminity. Here is the answer from dear Mark Rutland.

https://lkml.org/lkml/2020/3/23/598

Multiple clusters can be in the same Inner Shareable domain, and Linux relies on this being the case for systems it supports. It's possible to build a system where clusters are in distinct Inner Shareable domains, but Linux does not support using all cores on such a system.

Even with CCI, CCN, CMN, etc, Linux requires that all cores (which it is told about) are in the same Inner Shareable domain. That is what is commonly built.

© 2022 - 2024 — McMap. All rights reserved.