I've been trying to learn RISC-V coming from MIPS and initially they don't look to dissimilar, especially the instruction set. Are there any significant differences between the two? Are most of the differences in the backend?

According to Section 2.16 of Patterson, D. A., & Hennessy, J. L. (2018). Computer organization and design: The hardware/software interface. Cambridge, MA: Morgan Kaufmann Publishers. (RISC-V edition):

One of the main differences between RISC-V and MIPS is for conditional branches other than equal or not equal. Whereas RISC-V simply provides branch instructions to compare two registers, MIPS relies on a comparison instruction that sets a register to 0 or 1 depending on whether the comparison is true. Programmers then follow that comparison instruction with a branch on equal to or not equal to zero depending on the desired outcome of the comparison. Keeping with its minimalist philosophy, MIPS only performs less than comparisons, leaving it up to the programmer to switch order of operands or to switch the condition being tested by the branch to get all the desired outcomes. MIPS has both signed and unsigned versions of the set on less than instructions: slt and sltu.

When we look beyond the core instructions that are most commonly used, the other main difference is that the full MIPS is a much larger instruction set than RISC-V [...]

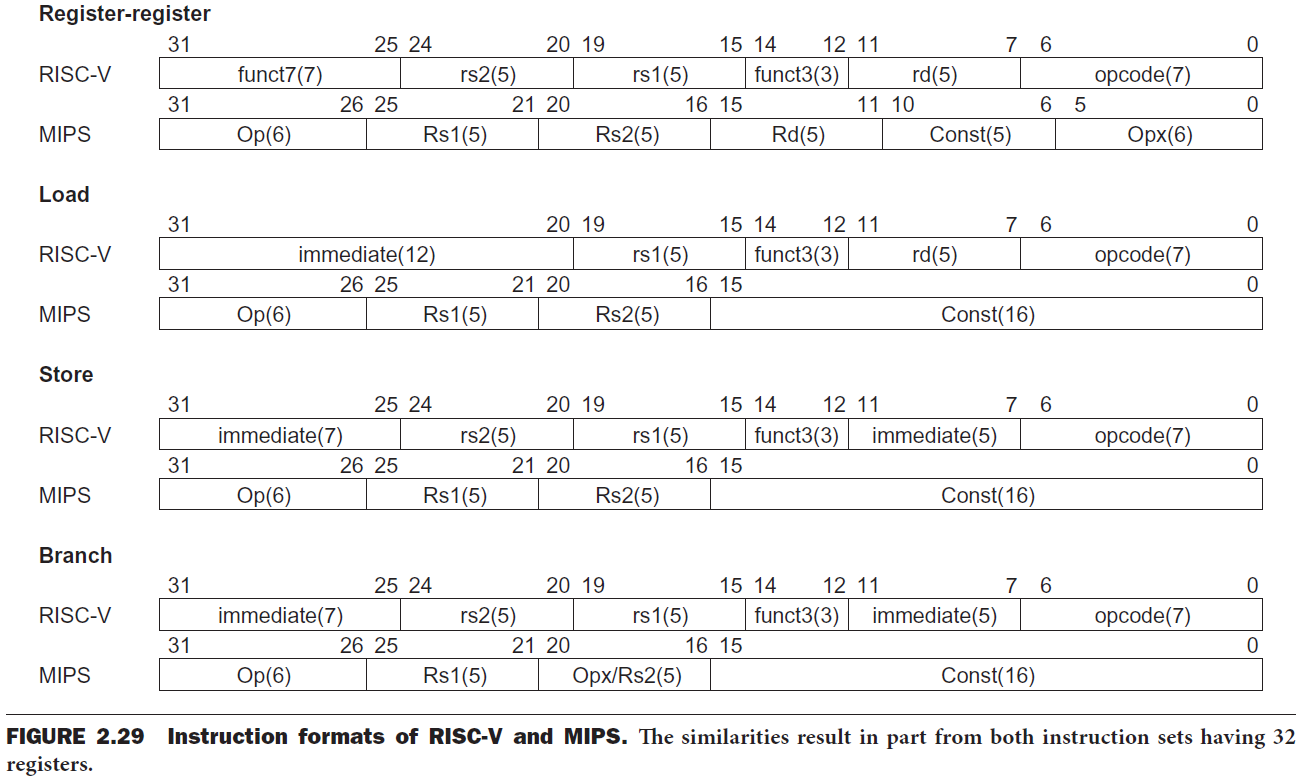

Figure 2.29 from the book shows the slight differences in instruction formats for the MIPS and the RISC-V:

One thing I want to add that is a bit more specific is that Immediate instructions with RISC-V use the upper 20 bits as compared to the upper 16 bit in MIPS.

For example in MIPS:

lui S0, 0x1234

S0 = 0x1234 0000

And in RISC-V its S0 = 0x0123 4000

© 2022 - 2024 — McMap. All rights reserved.